# Introduction aux systèmes informatiques Introduction générale

#### Michel Salomon

IUT de Belfort-Montbéliard Département d'informatique

## Objectifs et organisation

#### Objectifs

- Savoir utiliser un (des) système(s) informatique(s);

- 2 en appréhender le fonctionnement

#### Organisation

- Module en deux parties

- Système d'exploitation (7 sem. M. Fouzi)

- 2 Fonctionnement interne d'un ordinateur (6 sem. M. Salomon)

- Modalités de Contrôle des Connaissances

- Chaque partie comptera pour 50% de la note du module

- Au moins 2 contrôles dans cette partie

#### Décrire ce qu'est un ordinateur n'est pas aisé

- Grande variété d'ordinateurs

- Netbook

- Tablette tactile

- etc.

- Super-ordinateur

- Rapidité des évolutions technologiques

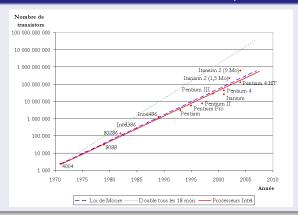

Illustration par la Loi de Moore (1975)

- Postulait initialement le doublement du nombre de transistors des microprocesseurs tous les 2 ans;

- entre 1971 et 2001 doublement tous les 1,96 années;

- "relativement" exacte jusqu'en 2012, depuis ralentissement (phénomène quantique : effet tunnel → limite de miniaturisation);

- version plus commune : doublement d'une grandeur (puissance, capacité, etc.) tous les 18 à 24 mois

On approche des limites de la technologie actuelle des semi-conducteurs Our limit to visibility goes out ~10 years TECHNOLOGY GENERATION 2017 2014 Beyond 2013 2007 2009 2011 2020 MANUFACTURING DEVELOPMENT Carbon Nanotube ~1nm diameter Graphene 1 atom thick **QW III-V Device** Nanowire Not to scale 10 atoms across

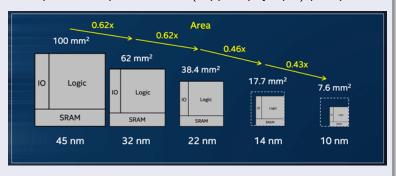

#### Pourquoi réduire la finesse de gravure?

#### Une gravure plus fine permet d'augmenter la densité des transistors

Une même micro-architecture (même nombre de transistors)

→ implémentée par un "Die" (support physique) plus petit

- Une même taille de "Die" (plus de transistors disponibles)

- → implémenter une micro-architecture plus performante

#### Loi de Moore versus nombre de transistors des proc. Intel (Wikipédia)

## Corollaire de la loi de Moore $\rightarrow$ loi de Wirth (1995)

Le logiciel ralentit plus vite que le matériel n'accélère

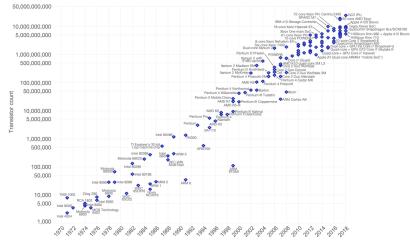

#### Moore's Law – The number of transistors on integrated circuit chips (1971-2018)

Moore's law describes the empirical regularity that the number of transistors on integrated circuits doubles approximately every two years. This advancement is important as other aspects of technological progress – such as processing speed or the price of electronic products – are linked to Moore's law.

Data source: Wikipedia (https://en.wikipedia.org/wiki/Transistor\_count)

The data visualization is available at OurWorldinData.org. There you find more visualizations and research on this topic.

Licensed under CC-BY-SA by the author Max Roser.

#### Domaine au croisement de nombreuses compétences

- Électronique

- Programmation système ou applicative

- Réseaux

- Mathématiques

- etc.

#### Nombreux principes de base communs à tout système informatique

- Le type et la représentation des informations

- La manière dont les composants internes dialoguent

- etc.

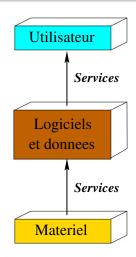

# Qu'est-ce qu'un système informatique?

Système informatique = ensemble de matériels et de logiciels

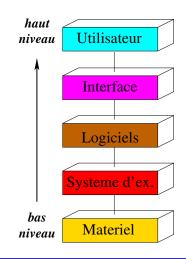

#### Description simplifiée en couches

- L'utilisateur dispose de services

- la navigation Internet Web;

- le traitement de texte :

- etc.

- grâce à des applications

- implémentées par des logiciels;

- traitant des données en entrée;

- produisant des données en sortie;

- exécuté(e)s "par" du matériel

# Qu'est-ce qu'un système informatique?

Système informatique = ensemble de matériels et de logiciels

#### Description évoluée en couches

- Ajout de couches intermédiaires

- Fonctionnalités étendues

- Isole les services "utilisateur" des couches de bas niveau

- L'interface

- Fenêtres

- Menus

- Aide contextuelle

- Le système d'exploitation

- Gestion de la mémoire

- Gestion des périphériques

- Arbitrage des ressources

# Qu'est-ce qu'un système informatique?

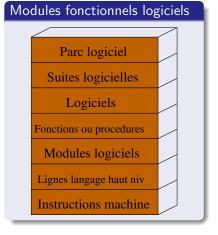

Système informatique = ensemble de matériels et de logiciels

# Modules fonctionnels matériels Internet Reseau local Ordinateur Cartes Circuits integres Portes logiques **Transistors** Semi-conduct

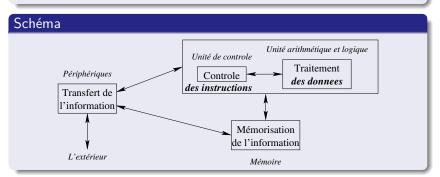

## Description fonctionnelle d'un système informatique

- Un système informatique manipule de l'information

- Un système informatique assure les fonctions suivantes :

- le traitement de l'information;

- la mémorisation de l'information ;

- le transfert de l'information ;

- le contrôle des opérations spécifiées par l'utilisateur via de l'information (un programme = suite d'instructions)

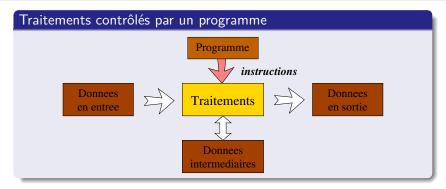

# Un système informatique est un système programmable

#### Traitements sur les données

- Calculs arithmétiques (addition, soustraction, etc.)

- Calculs booléens (et, ou, etc.)

- Rupture de séquence en fonction d'un résultat

- Mise en forme des données

#### Les prémices de l'ordinateur

- Mécanisation du calcul arithmétique

- Machine de Pascal (1642) : addition et soustraction ;

- Machine de Leibniz (1673) : ajoute division et multiplication

- Construction de machines commandées par des programmes

- Cartons perforés commandant un métier à tisser (1805)

- La machine analytique de Babbage (1833)

- Convergence des machines à calculer et commandées

- Premier calculateur programmable

- Contient l'essentiel des concepts des ordinateurs modernes

- Les théories mathématiques

- Système binaire introduit par Leibniz (1677)

- Algèbre de Boole (1854)

- Turing (1936) énonce les principes d'une machine théorique universelle en vue de définir le concept d'algorithme

- Shannon (1938) lie système binaire, algèbre de Boole et signaux électriques; popularise le terme *binary digit* (1948)

## Naissance de l'ordinateur - période 1939-1945

- Machines électromécaniques

- Z3 (1941) → machine digitale sans doute *Turing-complète*

- IBM (Harward) Mark 1 (1944)

- Premiers ordinateurs "électroniques"

- Atanasoff-Berry Computer (1942)  $\rightarrow$  non prog., pas *Turing-complet*

- ullet Colossus Mark 1 (1943), Mark 2 (1944) o pas Turing-complet

## Premier "vrai" ordinateur électronique : l'ENIAC (1943-1945)

## l'Electronic Numerical Integrator And Calculator

- Conçu par Eckert et Mauchly à l'Université de Pennsylvanie

- Entièrement électronique, programmable, Turing-complet

- Opérations réalisées dans des circuits électriques via des interrupteurs (tubes à vide) contrôlés électriquement

- 18000 tubes à vide, 30 tonnes et une surface de 72  $m^2$

- Multiplie 2 nombres de 10 chiffres en 3 millisecondes

Michel Salomon

## Colossus (à gauche) et ENIAC (à droite) (Wikipédia)

#### Avant fin 1945 John von Neumann propose une architecture (Turing - 1936)

- Architecture interne d'un calculateur universel (ordinateur)

- Définie en travaillant sur l'EDVAC avec Eckert et Mauchly

- Ordinateur à programme enregistré (instructions et données)

#### Invention du transistor en 1947

#### Générations d'ordinateur

- ullet  $1^{re}$  gén. d'ordinateur o utilisation de l'architecture dite de von Neumann

- Manchester Mark 1 (1949)

- l'Electronic Discrete Variable Automatic Computer (1949)

- Apparition de supports de stockage et du terme "ordinateur"

- ullet 2<sup>e</sup> gén. d'ordinateur o intégration des transistors

- TRADIC des Bell Labs (1954)

- IBM 7044 (1958) avec 64 Koctets de mémoire

- Apparation du terme "informatique" (information automatique)

- $3^e$  gén. d'ordinateur  $\rightarrow$  utilisation de circuits intégrés

- 4<sup>e</sup> gén. d'ordinateur → microprocesseur

- Intel 4004 (1971) avec 2300 transistors

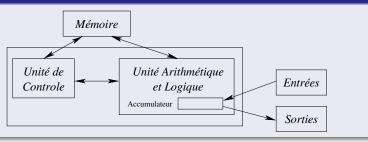

## Architecture de von Neumann

#### Caractéristiques de l'ordinateur

- Une machine universelle contrôlée par un programme

- Instructions et données sont codées sous forme binaire et enregistrées en mémoire

- Programme pouvant "modifier" ses instructions

- Exécutées en séquence (une après l'autre)

- mais existence d'instructions de rupture de séquence

- 5 composants essentiels :

- 1 une Mémoire

- contient instructions et données;

- 2 une Unité Arithmétique et Logique

- réalise les calculs;

- o une Unité de Contrôle ou de commande

- contrôle les opérations réalisées;

- 4 et des unités d'Entrées / Sorties

- permettent d'échanger des informations avec les périphériques

## Architecture de von Neumann

#### Schéma

#### L'Unité de Contrôle

- extrait une instruction de la mémoire;

- l'analyse;

- 3 recherche les données en mémoire;

- demande l'exécution de l'instruction dans l'UAL ou une E/S;

- o range le résultat dans la mémoire

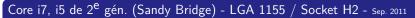

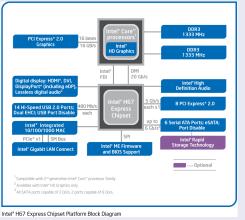

## Architecture des ordinateurs actuels

- Raffinement du schéma de von Neumann

- Accès "direct" à la mémoire par les périphériques

- On distingue 3 composants :

- 1'unité centrale de traitement (Central Processing Unit) ou processeur (on utilise également le terme microprocesseur)

- 2 la mémoire centrale ou principale

- Contient programmes et données

- Deux types de mémoire :

- mémoire morte (Read Only Memory) lecture seule

- mémoire vive (Random Access Memory) lecture/écriture

- 3 les interfaces d'Entrées/Sorties

- Lien entre le processeur et les périphériques externes/internes

- Périphériques :

- disque dur;

- carte graphique;

- etc.

Composants et périphériques reliés par des bus de communication

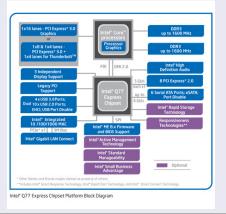

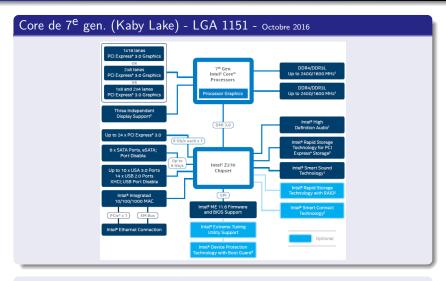

Core i7 de 1<sup>re</sup> gén. (Nehalem / Westmere) - LGA 1366 / Socket B - 2008 DDR3 memory 8.5 Gb/s Intel® Core™ i7 Processor DDR3 memory 8.5 Gb/s DDR3 memory 8.5 Gb/s OPI (25.6 GB/s) PCI Express\* 2.0 Graphics Support for up to Multi-card configurations: 36 lanes 1x16, 2x16, 4x8 or 2 GB/s DMI 12 Hi-Speed USB 2.0 Ports: RO Mh/s Intel®High Definition Audio Dual EHCI: USB Port Disable 6 Serial ATA Ports: eSATA: 6 PCI Express\* x1 Port Disable each x Intel® Integrated 10/100/1000 MAC Intel® Turbo Memory with User Pinning

Land Grid Array: proc. comportant une matrice de contacteurs

BIOS Support

Intel® Extreme Tuning

Support

Intel® Gigabit LAN Connect

Intel® X58 Express Chipset Block Diagram

···· Optional

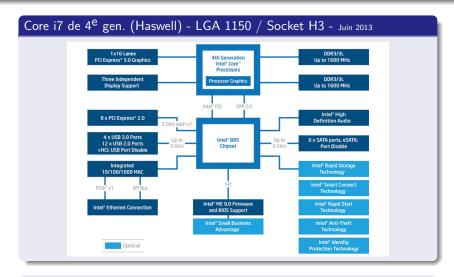

Puce réunissant contrôleur mémoire, cœur graphique et processeur

#### Core i7 de 3<sup>e</sup> gen. (Ivy Bridge) - LGA 2011 / Socket R - Avril 2012

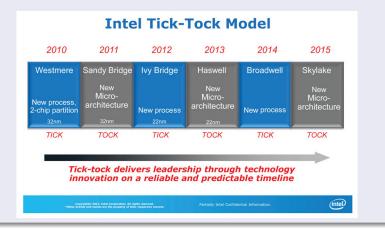

Sandy Bridge(-E)  $\rightarrow$  32 nm; Ivy Bridge  $\rightarrow$  22 nm

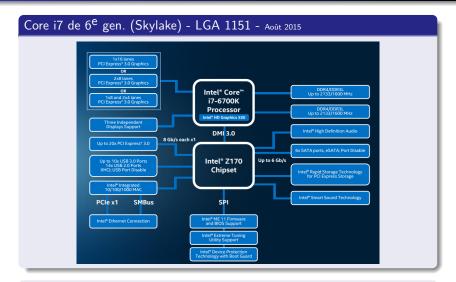

Gravure de 22 nm et optimisation de l'économie d'énergie

Gravure de 14 nm comme la 5<sup>e</sup> gen. (Broadwell)

Les récentes 8<sup>e</sup> et 9<sup>e</sup> gen. comportent plusieurs micro-architectures

# Core de 8<sup>e</sup> et 9<sup>e</sup> gen. (Coffee Lake Refresh) - LGA 1151 - Fin 2018 INTEL® Z390 CHIPSET BLOCK DIAGRAM

- ullet 8e gen. o Coffee Lake (14 nm++), Kaby Lake Refresh (14 nm++)

- ullet gen. o Coffee Lake Refresh (14 nm++), Cannon Lake (10 nm)

- $10^{\text{e}}$  gen.  $\rightarrow$ Ice Lake (10 nm+)

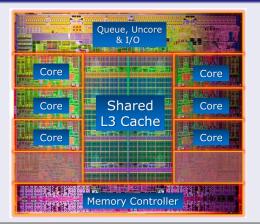

Proc. Core i7 3960X (Sandy E) - "Die" (support physique) du processeur

Q4'11 - Cache commun ightarrow 15 Mio ; Turbo Boost ightarrow 3/3/4/5/6/6

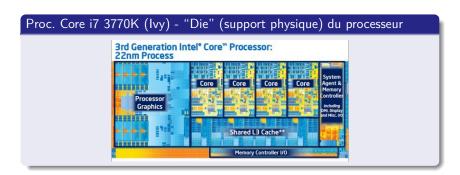

Q2'12 - Cache partagé ightarrow 8 Mio ; 3.5/3.9 GHz ; PCle Gen 3.0 ; 77 W

Ivy Bridge est le "Tick" associé au "Tock" Sandy Bridge

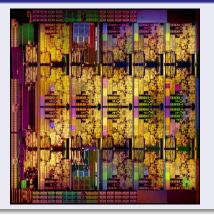

Proc. Core i7 5960X (Haswell-E) - "Die" (support physique) du proc.

Q3'14 - Cache partagé ightarrow 20 Mio ; 3.0/3.5 GHz ; PCle Gen 3.0 ; DDR4 ; 140 W

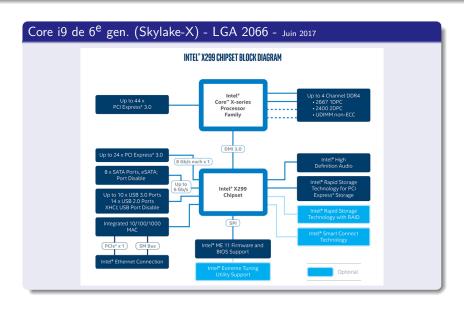

Proc. Core i9 7980XE (Skylake-X) - "Die" (support physique) du proc.

Q3'17 - Cache partagé ightarrow 24,75 Mio ; 2.60/4.4 GHz ; PCle Gen 3.0 ; DDR4 ; 165 W

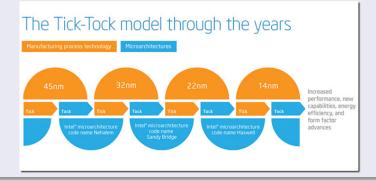

#### Modèle "Tick-Tock"

- Tick → évolution de la finesse de gravure (réduction du "die")

- Tock  $\rightarrow$  évolution de la micro-architecture

#### Modèle "Tick-Tock"

- Tick → évolution de la finesse de gravure (réduction du "die")

- Tock → évolution de la micro-architecture

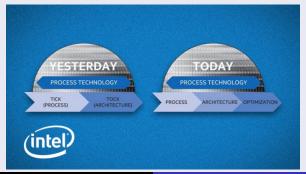

#### Intel met fin au modèle "Tick-Tock" en mars 2016

- Difficulté de mise en production de la gravure 10 nm

- Nombreuses "générations" avec la finesse de gravure 14 nm

- Optimisation portant surtout sur le multimédia

- Traitement de formats vidéos 10 bit H.265/HEVC, VP9

- etc.

#### Intel met fin au modèle "Tick-Tock" en mars 2016

- Difficulté de mise en production de la gravure 10 nm

- Nombreuses "générations" avec la finesse de gravure 14 nm

- Optimisation portant surtout sur le multimédia

- Traitement de formats vidéos 10 bit H.265/HEVC, VP9

- etc.

$8^{e}$  gen.  $\rightarrow$  Coffee Lake / Kaby Lake Refresh (14 nm), etc.  $9^{e}$  gen.  $\rightarrow$  Coffee Lake Refresh (14 nm), Cannon Lake (10 nm)

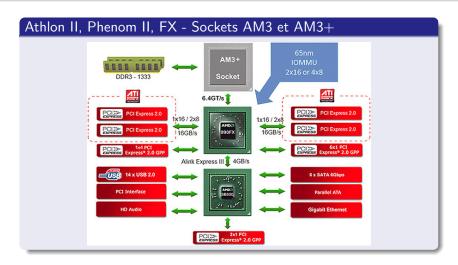

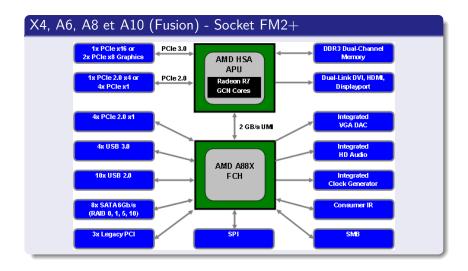

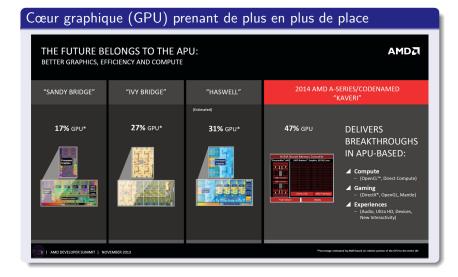

### Architecture d'une carte mère pour processeurs AMD

Objectif de l'intégration : réduire les coûts et maximiser les perf.

### Architecture d'une carte mère pour processeurs AMD

## Micro-architectures Piledriver (32 nm) et Steamroller (28 nm)

Proc. FX9590 (Piledriver - AM3+) - "Die" (support physique) du proc.

Q2'13 - Cache commun ightarrow 8 Mio ; Turbo Core ightarrow 4.7/4.8/5.0 GHz ; 220 W

# Micro-architectures Piledriver (32 nm) et Steamroller (28 nm)

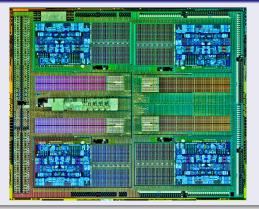

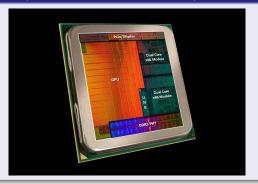

Proc. A10-7850K (Steamroller "Kaveri" - FM2+) - "Die" du proc.

Q1'14 - "Pas" de cache commun; 3.7/4.0 GHz; 95 W

# Micro-architectures Piledriver (32 nm) et Steamroller (28 nm)

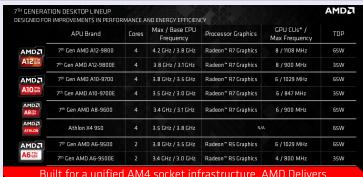

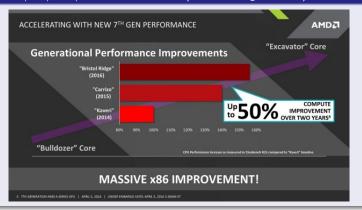

# Micro-architecture Excavator (28 nm)

#### Proc. A6/A8/A10/A12 et Athlon X4 (Bristol Ridge - AM4)

### Accelerated Processing Unit (CPU+Graphics Processing Unit)

- 2015 APU Carrizo → laptop et mobile; DDR3; ...

- 2016 APU Bristol Ridge et Stoney Ridge → DDR4; ...

### Micro-architecture Excavator (28 nm)

#### Proc. A6/A8/A10/A12 et Athlon X4 (Bristol Ridge - AM4)

### Accelerated Processing Unit (CPU+Graphics Processing Unit)

- 2017 Fin de Bulldozer Series (Bristol Ridge et Stoney Ridge)

- Depuis Zen Series (Ryzen  $\rightarrow$  desktop et Epyc  $\rightarrow$  server)

### Micro-architecture Zen (14 nm) - Desktop

#### Proc. Ryzen 3/5/7 (AM4) et Threadripper (TR4) - 14 nm et 12 nm

### Roadmap AMD pour les générations Zen

- ullet 2018 Zen+ (12 nm) / 2019 Zen 2 ightarrow 7 nm (I/O ightarrow 12 ou 14 nm)

- 2020/2021? Zen 3 (7 nm+) /? Zen 4 (6 nm)

Michel Salomon

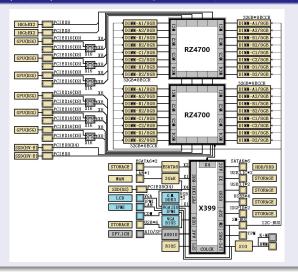

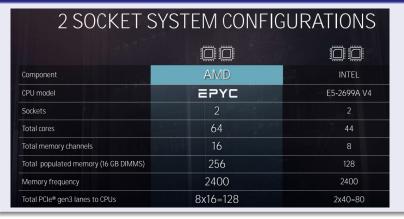

# Micro-architecture Zen (14 nm) - Datacenter / Server

### Proc. Epyc (Naples) - exemple de diagramme bi-proc. avec chipset X399

### Micro-architecture Zen (14 nm) - Datacenter / Server

### Proc. Epyc (Naples) - plateforme concurrente du Xeon d'Intel

AMD **S**ystem **O**n **C**hip  $\rightarrow$  intégration de fonctionnalités du *chipset*

# Micro-architecture Zen2 (7 nm) - Datacenter / Server

#### Proc. Epyc (Rome) versus Proc. Intel Xeon Cascade Lake

**EPYC 7742**

- 64 cœurs 225 W

(8 chiplets de 8 cœurs)

- 58.5 mm × 75.4 mm

- coût > 7000\$

Xeon Platinum 9282

- 56 cœurs 400 W

- 76.0 mm × 72.5 mm

- coût > 10000 \$?

Passage d'une architecture monolitique au multi-die

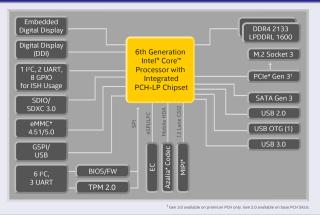

## Plateforme embarquée / mobile (System on Chip)

### Processeur de type Intel Skylake-U

Intégration poussée à l'extrême o disparition du *chipset*

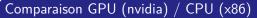

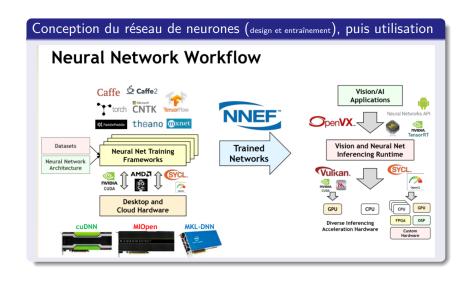

### Utilisation de GPUs pour du calcul haute performance

### Utilisation en intelligence artificielle

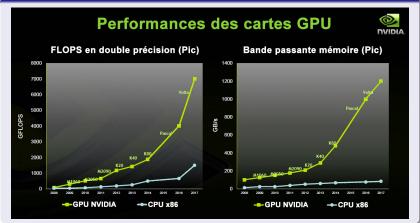

Implémentation de réseaux de neurones profonds (Deep Learning)

### Qu'est-ce que le Deep Learning?

Illustration : problème de reconnaissance / classification d'image

### Qu'est-ce que le Deep Learning?

### Processeurs optimisés pour le Deep Learning

### Émergence de nombreux processeurs spécialisés - Al-focused chips

- Intel Nervana Neural Network Processors (NNP)

- Google Tensor Processing Unit (TPU)

- Amazon AWS Inferentia

- NVIDIA Deep Learning Accelerator (NVDLA)

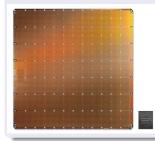

- Cerebras Wafer Scale Engine (WSE)

- 21,5 cm de large

- 400000 cœurs et 18 Gio de mémoire

- 56 fois plus grand que le plus grand GPU actuel

- 1200 milliards de transistors (GPU 21,1 milliards)

### Plan du cours

- Introduction générale

- 2 Représentation interne des informations

- Codage des entiers et arithmétique associée

- Codage des réels

- Codage des caractères

- Structure d'un ordinateur